# CMX7143 Multi-Mode Wireless Data Modem

D/7143\_FI2.0/10 May 2013

## **DATASHEET**

Provisional Issue

#### 7143FI-2.x 4FSK Packet Data Modem

#### **Features**

- Multiple Modulation Types

- o 7143 FI-1.0: GMSK/GFSK Modulation

- 7143 FI-2.0: 4FSK Modulation Over-air compatibility with CMX969 for RD-LAP Tx/Rx

- o 7143 FI-3.0: FFSK/MSK Modulation

- Automatic Frame Sync Detection

- Automatic Preamble, Frame Sync Insertion

- 2 x Auxiliary ADCs and 4 x Auxiliary DACs

- 3 x Analogue Inputs (RSSI or Discriminator)

- C-BUS Serial Interface to Host µController

- Flexible Bit Rates

- Raw Mode, Data Pump, Carrier Sense

- Auxiliary System Clock Outputs

- Tx Outputs for 2-point or I/Q Modulation

- Available in 48-pin LQFP and VQFN Packages

- Low-power 3.3V Operation

- Flexible Powersave Modes

- Formatted or Raw Data Modes

- Soft Decision Data Bits

## 1 Brief Description

Designed for use in wireless data modems, the CMX7143 with 7143FI-2.x is a half-duplex modem with carrier sense and automatic control of transmit hardware, including a RAMDAC for PA ramping. Carrier sense provides a listen before talk capability, automatically reverting to receive if activity on channel is detected. In receive, automatic frame sync detection provides acquisition of the received signal with minimal host intervention. Two different frame sync patterns may be searched for concurrently, with little need for preamble.

Continued...

Other features include two Auxiliary ADC channels with four selectable inputs and up to four auxiliary DAC outputs (with an optional RAMDAC on the first DAC output, to facilitate transmitter power ramping).

Coded mode supports block types compatible with the CMX919 and CMX969 (RD-LAP) modems.

The device has flexible powersaving modes and is available in both LQFP and VQFN packages.

The device utilises CML's proprietary  $FirmASIC^{\circledR}$  component technology. On-chip sub-systems are configured by a Function Image<sup>TM</sup>: this is a data file that is uploaded during device initialisation and defines the device's function and feature set. The Function Image<sup>TM</sup> can be loaded automatically from an external EEPROM or from a host  $\mu$ Controller over the built-in C-BUS serial interface. The device's functions and features can be enhanced by subsequent Function Image<sup>TM</sup> releases, facilitating in-the-field upgrades. This document refers specifically to the features provided by Function Image<sup>TM</sup> 7143FI-2.x. Separate Function Image<sup>TM</sup> are available which support GFSK/GMSK and FFSK/MSK modulation.

This Datasheet is the first part of a two-part document comprising Datasheet and User Manual: the User Manual can be obtained by registering your interest in this product with your local CML representative.

## **CONTENTS**

| C = =4:      |         |                | CONTENTS                                              | Daga        |  |  |  |  |

|--------------|---------|----------------|-------------------------------------------------------|-------------|--|--|--|--|

| <u>Secti</u> |         |                |                                                       | <u>Page</u> |  |  |  |  |

| 1            | Brief [ | Desc           | ription                                               | 1           |  |  |  |  |

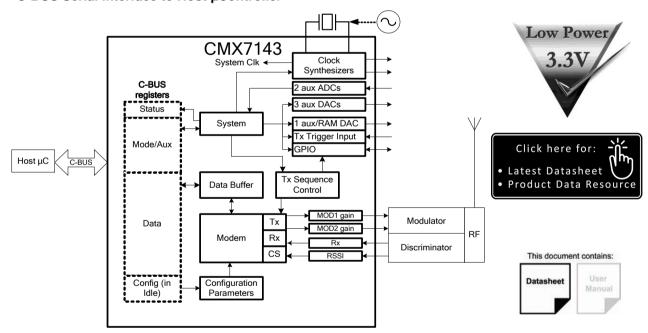

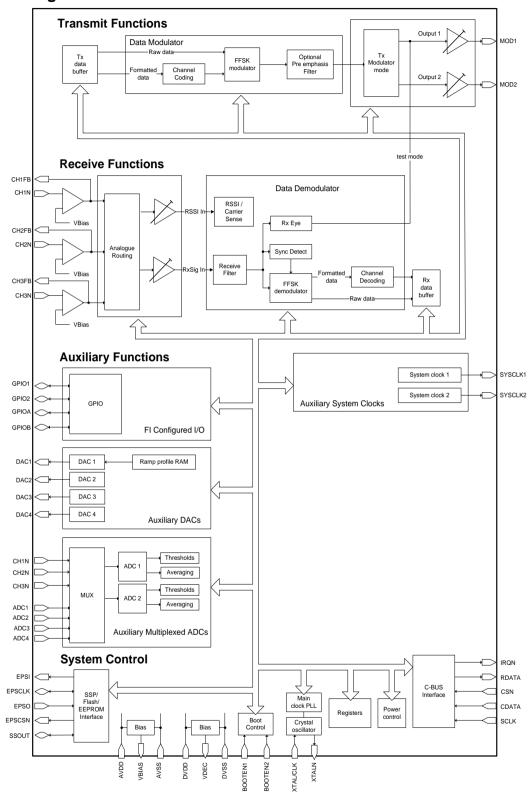

| 2            | Block   | Block Diagram7 |                                                       |             |  |  |  |  |

| 3            | Signal  | Signal List8   |                                                       |             |  |  |  |  |

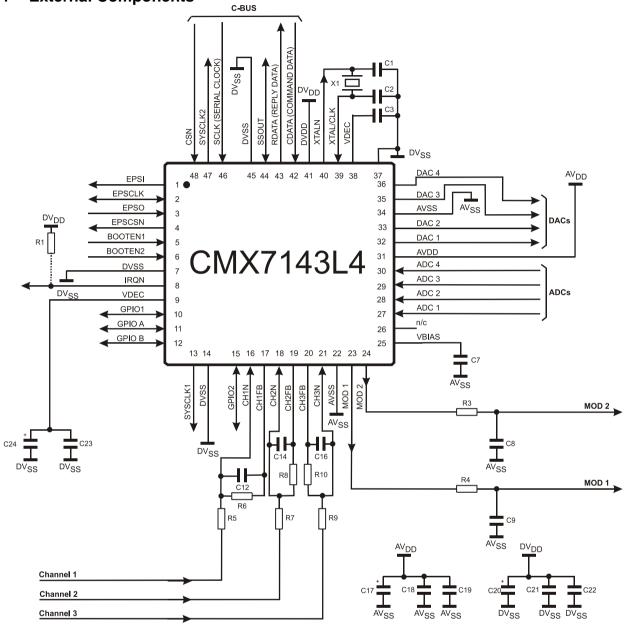

| 4            | Exterr  | nal C          | omponents                                             | 10          |  |  |  |  |

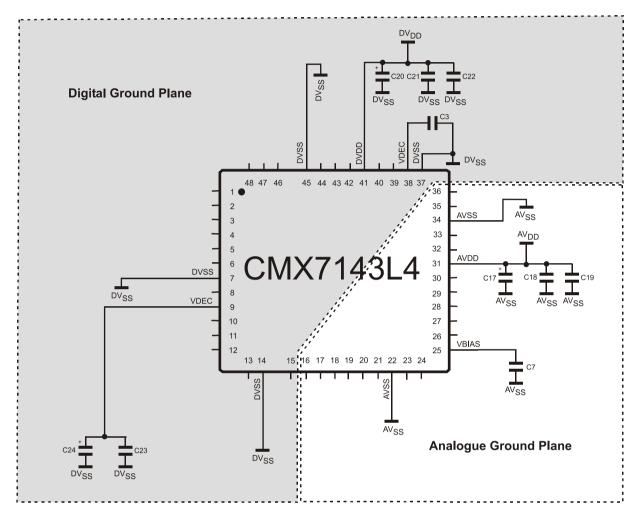

| 5            | PCB L   | .ayoı          | ut Guidelines and Power Supply Decoupling             | 12          |  |  |  |  |

| 6            | Gener   | al Da          | escription                                            | 13          |  |  |  |  |

| Ū            | 6.1     |                | /X7143 Features                                       |             |  |  |  |  |

| _            | _       |                |                                                       |             |  |  |  |  |

| 7            |         |                | escriptions                                           |             |  |  |  |  |

|              | 7.1     |                | al Frequency                                          |             |  |  |  |  |

|              | 7.2     |                | st Interface                                          |             |  |  |  |  |

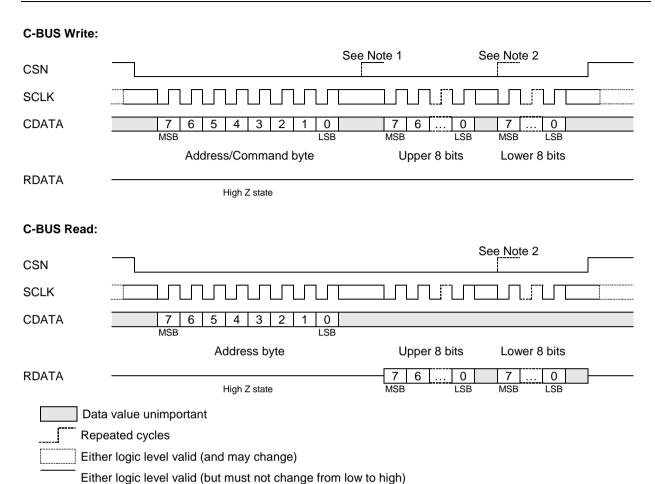

|              |         | 2.1            | C-BUS Operation                                       |             |  |  |  |  |

|              | 7.3     |                | nction Image™ Loading                                 |             |  |  |  |  |

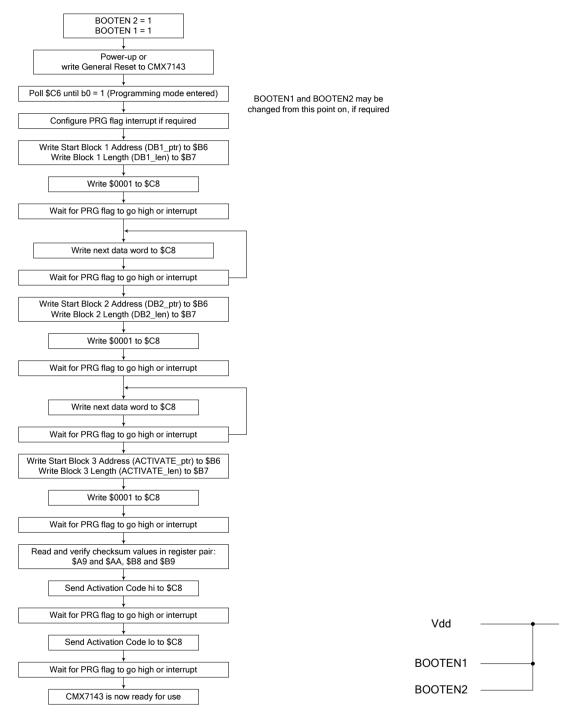

|              |         | 3.1            | FI Loading from Host Controller                       |             |  |  |  |  |

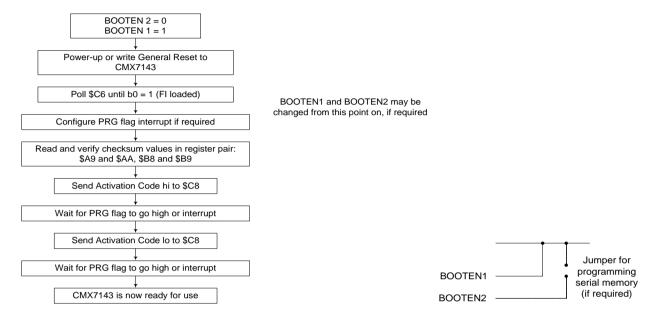

|              |         | 3.2            | FI Loading from Serial Memory                         |             |  |  |  |  |

|              | 7.4     |                | vice Control                                          |             |  |  |  |  |

|              |         | 4.1            | Normal Operation Overview                             |             |  |  |  |  |

|              |         | 4.2            | Device Configuration (Using the Programming register) |             |  |  |  |  |

|              |         | 4.3            | Device Configuration (Using dedicated registers)      |             |  |  |  |  |

|              |         | 4.4            | Interrupt Operation                                   |             |  |  |  |  |

|              |         | 4.5            | Signal Routing                                        |             |  |  |  |  |

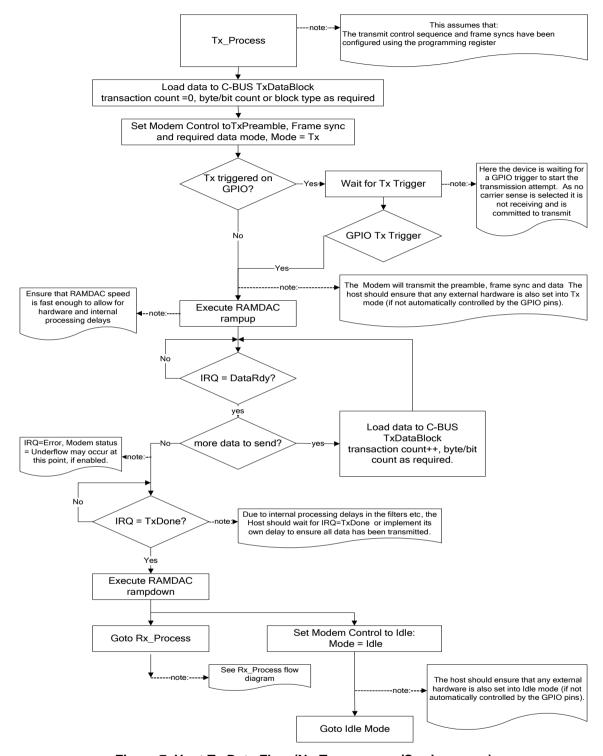

|              |         | 4.6            | Tx Mode                                               |             |  |  |  |  |

|              | 7.4     | 4.7            | Rx Mode                                               |             |  |  |  |  |

|              | 7.4     | 4.8            | Carrier Sense Mode                                    |             |  |  |  |  |

|              | 7.4     | 4.9            | The Transmit Sequence                                 |             |  |  |  |  |

|              | 7.4     | 4.10           | Other Modem Modes                                     | 27          |  |  |  |  |

|              | 7.4     | 4.11           | Data Transfer                                         | 28          |  |  |  |  |

|              | 7.4     | 4.12           | Raw Data Transfer                                     | 29          |  |  |  |  |

|              | 7.4     | 4.13           | Formatted Data Transfer                               | 29          |  |  |  |  |

|              | 7.4     | 4.14           | Pre-loading Transmit Data                             | 29          |  |  |  |  |

|              | 7.4     | 4.15           | Auxiliary Clock Rates                                 | 29          |  |  |  |  |

|              | 7.4     | 4.16           | Auxiliary Data                                        | 30          |  |  |  |  |

|              | 7.4     | 4.17           | GPIO Pin Operation                                    | 30          |  |  |  |  |

|              | 7.4     | 4.18           | Auxiliary ADC Operation                               | 30          |  |  |  |  |

|              | 7.4     | 4.19           | Auxiliary DAC/RAMDAC Operation                        | 31          |  |  |  |  |

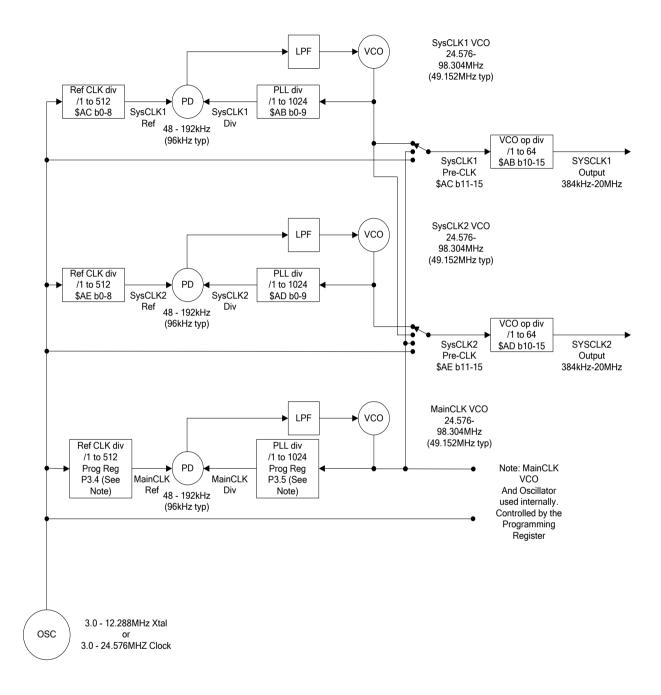

|              | 7.5     | Dig            | gital System Clock Generators                         | 32          |  |  |  |  |

|              | 7.5     | 5.1            | System Clock Operation                                | 33          |  |  |  |  |

|              | 7.5     | 5.2            | Main Clock Operation                                  | 33          |  |  |  |  |

|              | 7.6     | Sig            | nal Level Optimisation                                | 33          |  |  |  |  |

|              | 7.6     | 3.1            | Transmit Path Levels                                  | 33          |  |  |  |  |

|              | 7.6     | 5.2            | Receive Path Levels                                   | 33          |  |  |  |  |

|              | 7.7     | C-E            | BUS Register Summary                                  | 34          |  |  |  |  |

| 8        | 7143FI-2.x Features                                                            | 35          |

|----------|--------------------------------------------------------------------------------|-------------|

|          | 8.1 Modulation                                                                 | 35          |

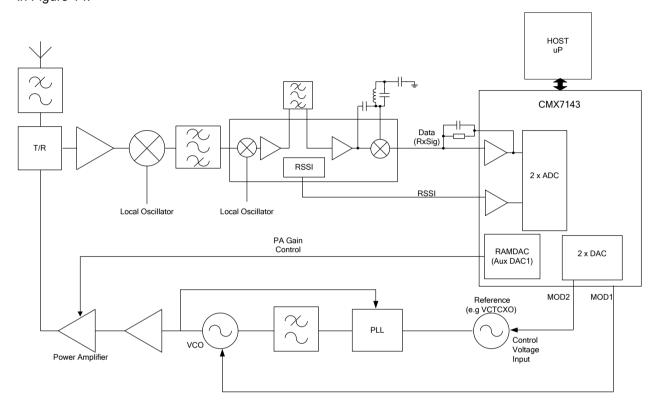

|          | 8.2 Radio Interface                                                            | 36          |

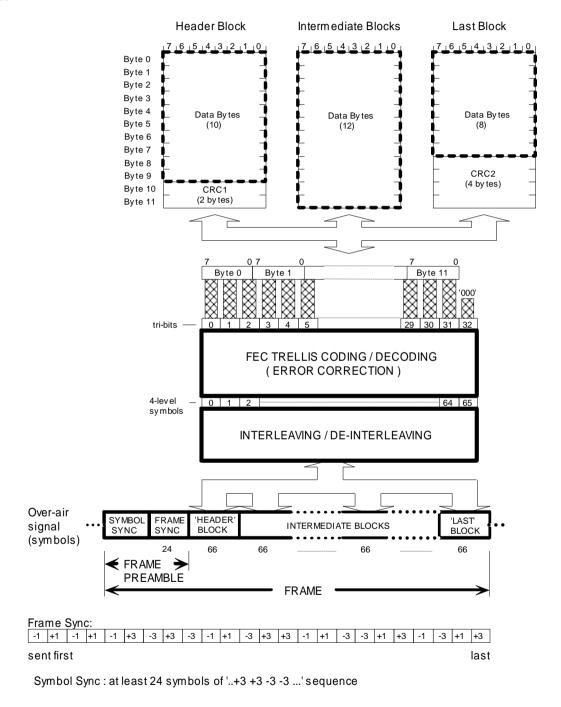

|          | 8.3 Formatted Data                                                             | 37          |

|          | 8.4 Cyclic Redundancy Codes                                                    | 40          |

|          | 8.5 Transmit Performance                                                       |             |

|          | 8.6 Receive Performance                                                        | 47          |

| 9        | Performance Specification                                                      | 48          |

| _        | 9.1 Electrical Performance                                                     |             |

|          | 9.1.1 Absolute Maximum Ratings                                                 |             |

|          | 9.1.2 Operating Limits                                                         |             |

|          | 9.1.3 Operating Characteristics                                                |             |

|          | 9.1.4 Parametric Performance                                                   |             |

|          | 9.2 C-BUS Timing                                                               |             |

|          | 9.3 Packaging                                                                  |             |

| <b>-</b> |                                                                                | _           |

| Tabl     |                                                                                | <u>Page</u> |

|          | able 1 BOOTEN Pin States                                                       |             |

|          | able 2 C-BUS Data Registers                                                    |             |

| Ta       | able 3 C-BUS Registers                                                         | 34          |

| Figu     | ıre                                                                            | Page        |

|          |                                                                                |             |

|          | gure 1 Block Diagram                                                           |             |

|          | gure 2 CMX7143 Recommended External Components                                 |             |

|          | gure 3 CMX7143 Power Supply and De-couplinggure 4 C-BUS Transactions           |             |

|          | •                                                                              |             |

|          | gure 5 FI Loading from Host                                                    |             |

|          | gure 6 FI Loading from Serial Memory                                           |             |

|          | gure 7 Host Tx Data Flow (No Tx sequence/Carrier sense)                        |             |

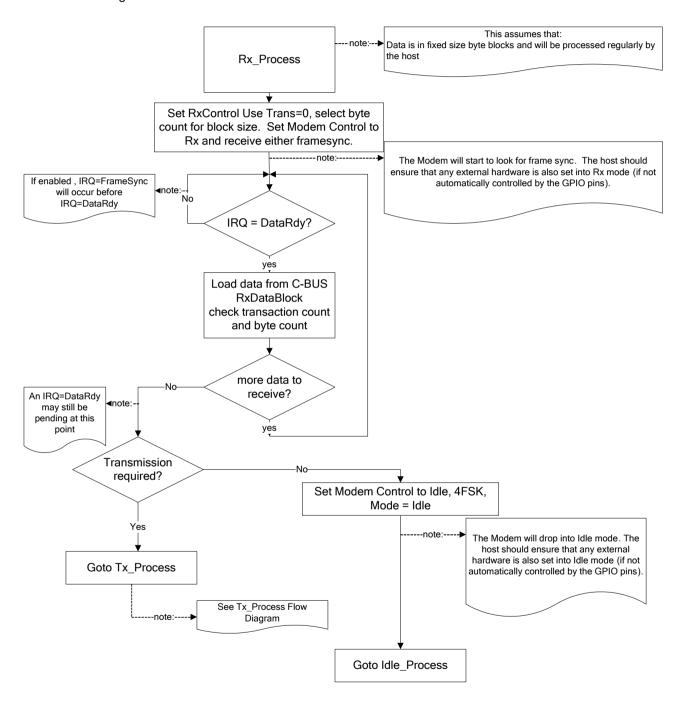

|          | gure 8 Host Rx Data Flow (Use Trans=0)                                         |             |

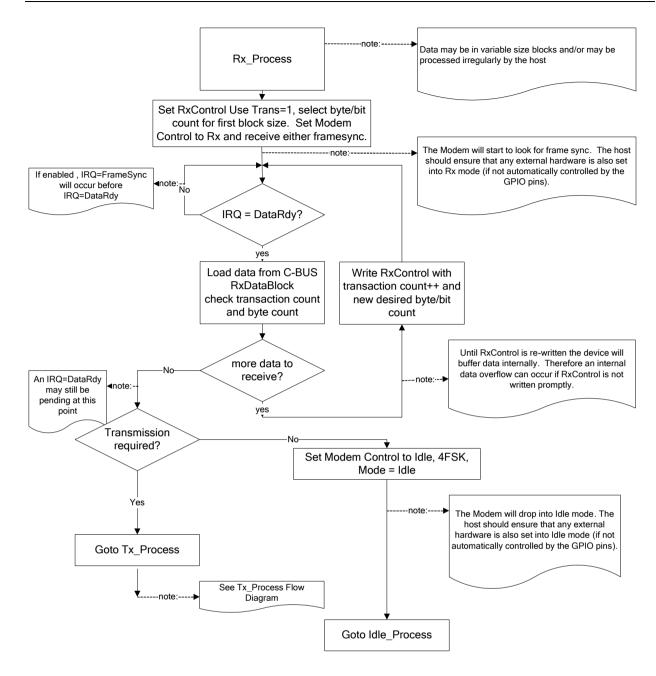

|          | gure 9 Host Rx Data Flow (Flow controlled data with UseTrans=1)                |             |

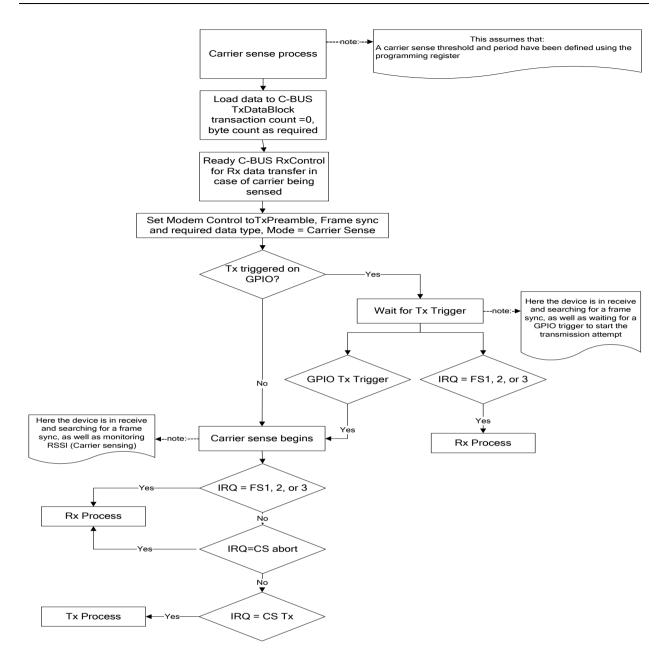

|          | gure 10 Carrier Sense                                                          |             |

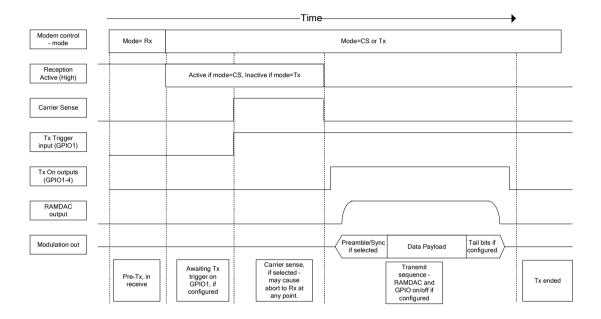

|          | gure 11 Transmit Sequence                                                      |             |

|          | gure 12 Digital Clock Generation Schemes                                       |             |

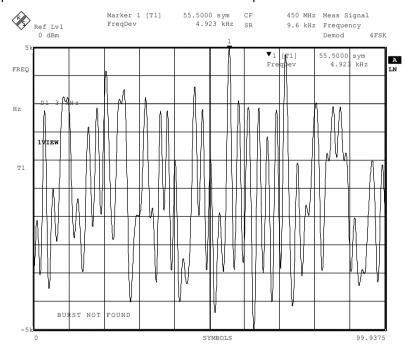

|          | gure 13 4FSK PRBS Waveform                                                     |             |

|          | gure 14 Outline Radio Design                                                   |             |

|          | gure 15 Formatted Data Over Air Signal Format                                  |             |

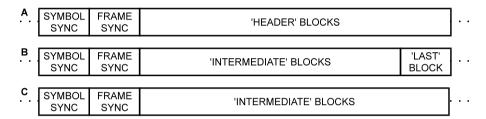

| ,        | gure 16 Some Alternative Frame Structures                                      |             |

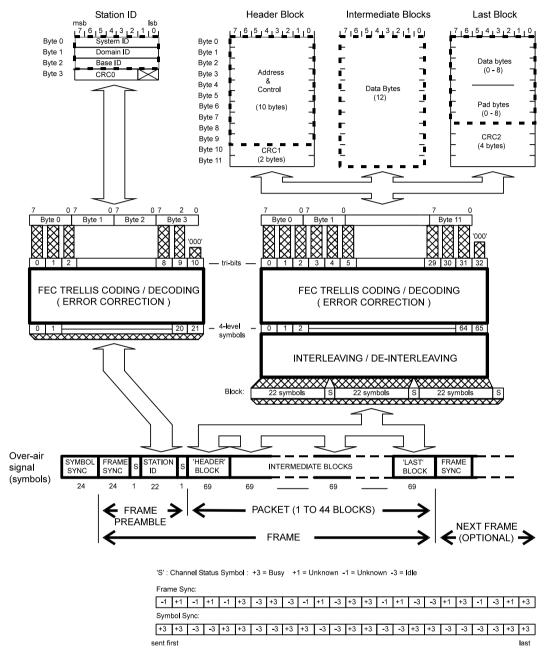

|          | gure 17 RD-LAP Over Air Signal Format                                          |             |

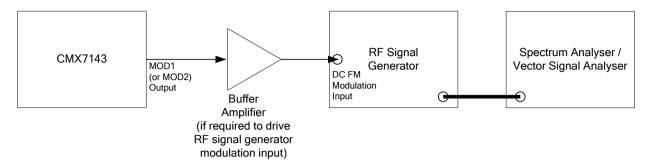

| Fig      | gure 18 Tx Spectrum and Modulation Measurement Configuration                   | 41          |

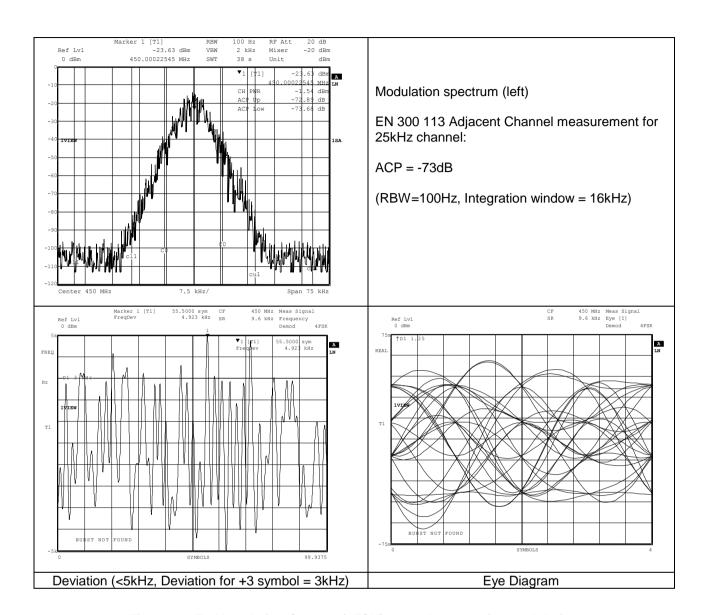

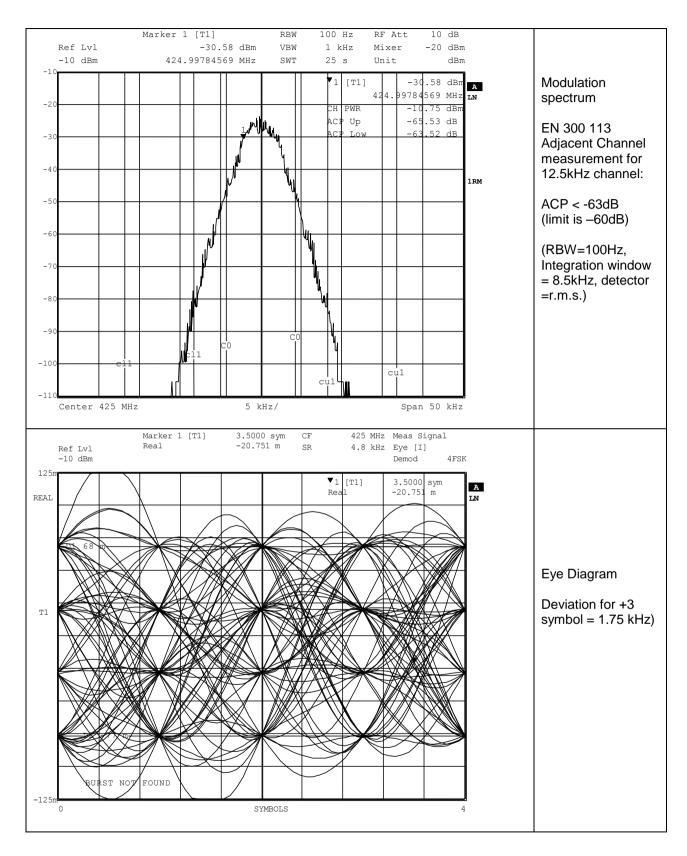

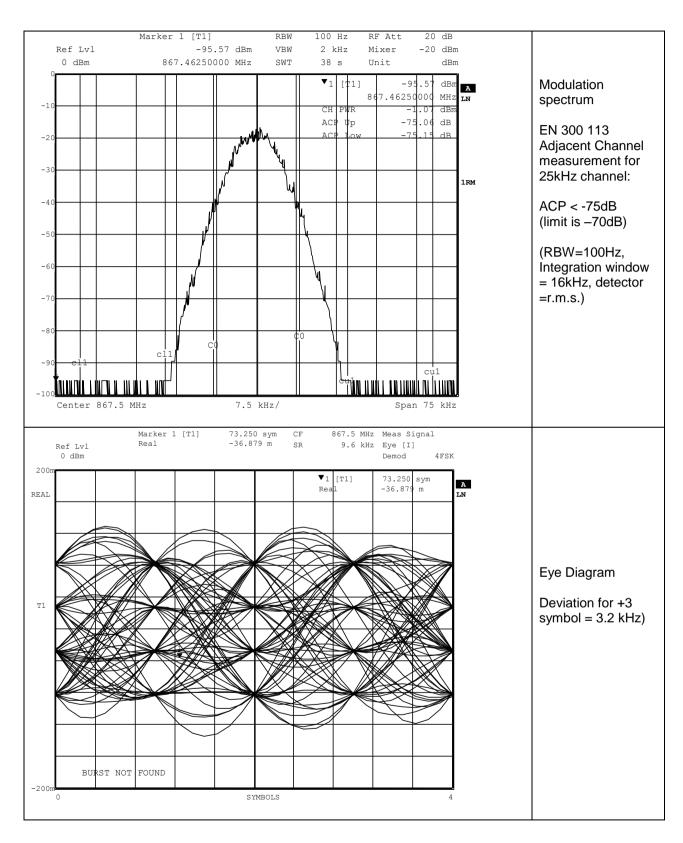

| Fig      | gure 19 Tx Modulation Spectra (4FSK), 19200bps, 2-point modulation             | 42          |

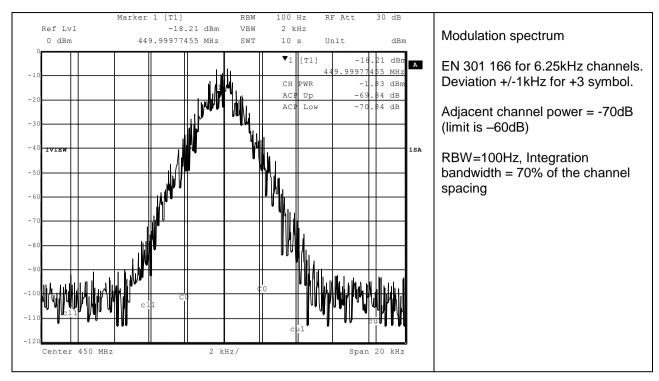

| Fi       | gure 20 Tx Modulation Spectra (4FSK), 9600bps (4800 symb/s), 2point modulation | 43          |

| Fig      | gure 21 Tx Modulation Spectra (4FSK), 4800bps – 2-point modulation             | 44          |

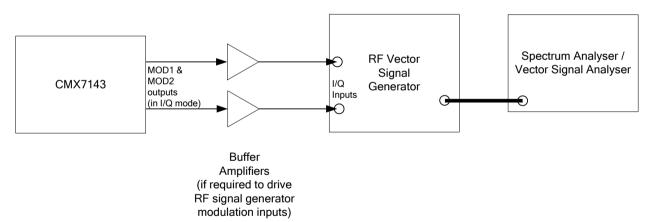

| Fig      | gure 22 Tx Spectrum and Modulation Measurement Configuration for I/Q Operation | 44          |

|          | gure 23 Tx Modulation Spectra (4FSK), 9600bps (4800 symb/s), I/Q modulation    |             |

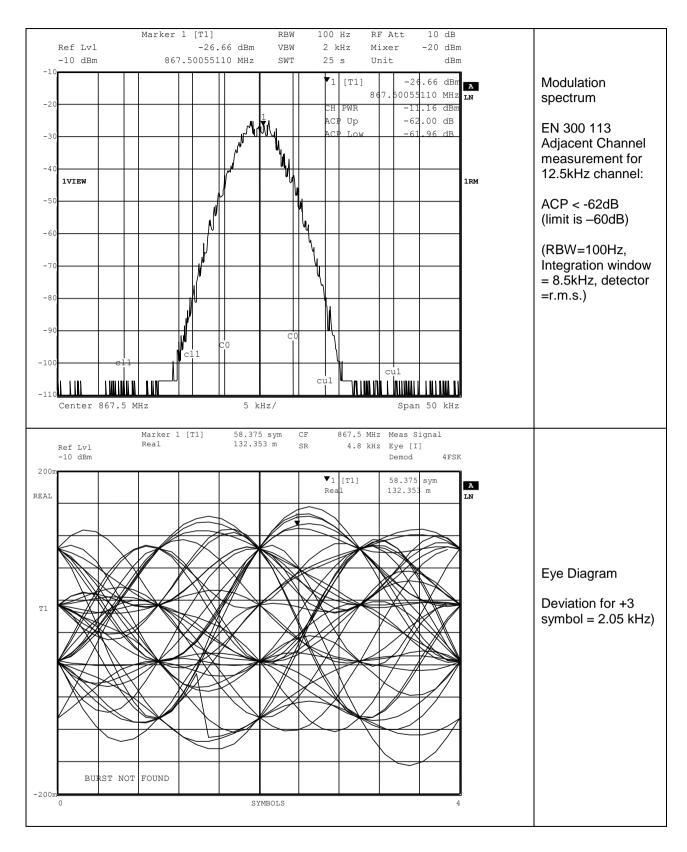

|          | gure 24 Tx Modulation Spectra (4FSK), 19200bps (9600 symb/s), I/Q modulation   |             |

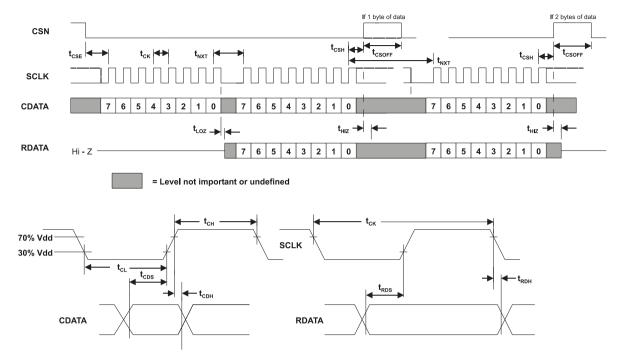

|          | gure 25 C-BUS Timing                                                           |             |

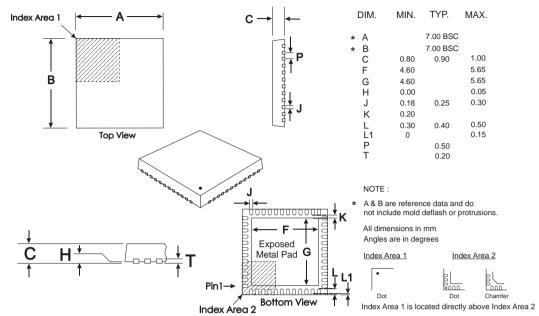

| Figure 26 | Mechanical Outline of 48-pin VQF | N (Q3)50 | 6 |

|-----------|----------------------------------|----------|---|

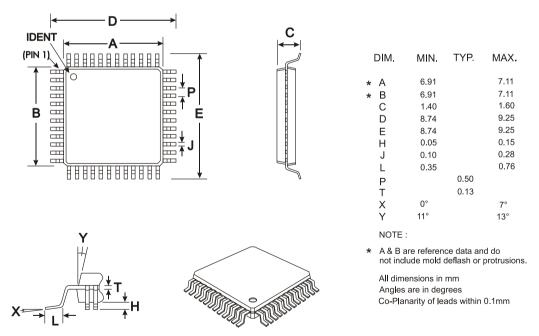

| Figure 27 | Mechanical Outline of 48-pin LQF | P (L4)   | 6 |

It is always recommended that you check for the latest product datasheet version from the CML website: <a href="mailto:www.cmlmicro.com">www.cmlmicro.com</a>].

## <u>History</u>

| Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| 10      | Added RD-LAP channel coding block types in FI-2.x.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |  |  |

| 9       | <ul> <li>Clarification of BOOTEN options by Table 1 and Table 4.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26.7.11  |  |  |

|         | Correction of error in Figure 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |

| 8       | <ul> <li>Clarification of P4.x program block nomenclature and minor typographical</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01.12.09 |  |  |

|         | errors. Clarification of maximum bit/byte counter value in raw mode (TxData 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |

|         | and RxData 0). Definition of the action of any unused bits added. Default pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |  |  |

| 7       | amble length in P0.8 corrected to 18 symbols.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00.40.00 |  |  |

| 7       | Additional information about CRC2 Reset, Insert Preamble, insert FS1 and insert FS2 features added in 7143 FL 2.1.2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 06.10.09 |  |  |

|         | insert FS2 features added in 7143FI-2.1.2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |

|         | <ul> <li>Clarification of additional delay required when preloading data in Tx Idle or CS<br/>Idle modes, in section 7.4.14, and additional delays for all consecutive C-BUS</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |

|         | writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |

| 6       | Changes to Pin names, Register and Bit names for consistency with other Fls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31.07.09 |  |  |

|         | (Functionality is unchanged, but drawings, tables and text descriptions updated).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |  |  |

|         | Addition of a "Last tail" status bit in Tx for 7143FI-2.1.1.0. Description added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |  |  |

|         | Table in section 11.1 replaced by a hyperlinked register table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |  |  |

|         | <ul> <li>Descriptions of the b1512 allocation in section 11.2.4 corrected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |  |  |

|         | Definition of maximum signal levels clarified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |  |  |

|         | <ul> <li>Details of Fine output attenuation in Program Blocks P4.9 and P4.10 added.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |  |  |

|         | <ul> <li>FI loading procedure, P3.x tables and Reset mechanisms clarified.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |  |  |

|         | <ul> <li>Style of EDS changed to conform to latest guidelines, logos, etc. also updated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |

|         | Document is now "Provisional Issue".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |

| 5       | Changes to Program Block P4.1 specification to allow for selection of Tx      DROCK TO BROCK THE TRANSPORT OF TRANSPORT THE | 04.02.09 |  |  |

|         | RRC+Sinc and an Rx RRC+Inverse Sinc filter OR RRC for both Tx and Rx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |  |  |

|         | <ul> <li>Changes to Program Block P4.1 specification to allow for selection of soft bit<br/>outputs in raw mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |  |  |

|         | <ul> <li>Changes to the description of RxData registers and RxControl register to define</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |

|         | soft output operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |  |

|         | <ul> <li>Error in power up bit specification corrected (Power Down Control register).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |

|         | Added explanation of RSSI and inverted P4.7 and P4.8 in Program Blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |

|         | Minor typographical corrections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |

| 4       | Correction in rates that the host should read/write Aux Data Control registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17.06.08 |  |  |